## **DSP Microcomputer**

# ADSP-2187L

#### FEATURES

PERFORMANCE

25 ns Instruction Cycle Time @ 3.3 Volts, 40 MIPS Sustained Performance

Single-Cycle Instruction Execution

Single-Cycle Context Switch

3-Bus Architecture Allows Dual Operand Fetches in Every Instruction Cycle

**Multifunction Instructions**

Power-Down Mode Featuring Low CMOS Standby Power Dissipation with 400 Cycle Recovery from Power-Down Condition

Low Power Dissipation in Idle Mode

#### INTEGRATION

- ADSP-2100 Family Code Compatible, with Instruction Set Extensions

- 160K Bytes of On-Chip RAM, Configured as 32K Words On-Chip Program Memory RAM and 32K Words On-Chip Data Memory RAM

- Dual Purpose Program Memory for Both Instruction and Data Storage

- Independent ALU, Multiplier/Accumulator, and Barrel Shifter Computational Units

**Two Independent Data Address Generators**

Powerful Program Sequencer Provides Zero Overhead Looping Conditional Instruction Execution

Programmable 16-Bit Interval Timer with Prescaler 100-Lead TQFP

#### SYSTEM INTERFACE

- 16-Bit Internal DMA Port for High Speed Access to On-Chip Memory (Mode Selectable)

- 4 MByte Memory Interface for Storage of Data Tables and Program Overlays (Mode Selectable)

- 8-Bit DMA to Byte Memory for Transparent Program and Data Memory Transfers (Mode Selectable)

- I/O Memory Interface with 2048 Locations Supports Parallel Peripherals (Mode Selectable)

Programmable Memory Strobe and Separate I/O Memory Space Permits "Glueless" System Design

**Programmable Wait State Generation**

Two Double-Buffered Serial Ports with Companding Hardware and Automatic Data Buffering

Automatic Booting of On-Chip Program Memory from Byte-Wide External Memory, e.g., EPROM, or Through Internal DMA Port

Six External Interrupts

13 Programmable Flag Pins Provide Flexible System Signaling

#### \*ICE-Port is a trademark of Analog Devices, Inc.

#### **REV. 0**

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

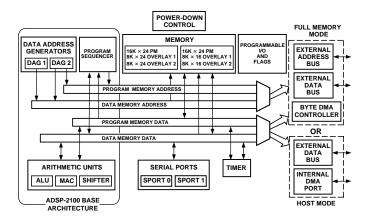

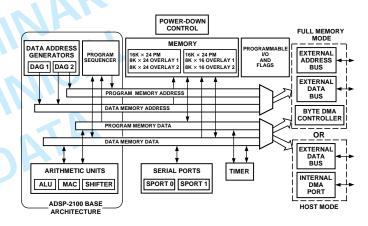

#### FUNCTIONAL BLOCK DIAGRAM

UART Emulation through Software SPORT Reconfiguration ICE-Port<sup>™</sup> Emulator Interface Supports Debugging in Final Systems

#### GENERAL NOTE

This data sheet represents preliminary (x- grade) specifications for the ADSP-2187L 3.3V processor.

#### **GENERAL DESCRIPTION**

The ADSP-2187L is a single-chip microcomputer optimized for digital signal processing (DSP) and other high speed numeric processing applications.

The ADSP-2187L combines the ADSP-2100 family base architecture (three computational units, data address generators and a program sequencer) with two serial ports, a 16-bit internal DMA port, a byte DMA port, a programmable timer, Flag I/O, extensive interrupt capabilities, and on-chip program and data memory.

The ADSP-2187L integrates 160K bytes of on-chip memory configured as 32K words (24-bit) of program RAM, and 32K words (16-bit) of data RAM. Power down circuitry is also provided to meet the low power needs of battery operated portable equipment. The ADSP-2187L is available in 100-lead TQFP package.

In addition, the ADSP-2187L supports new instructions, which include bit manipulations—bit set, bit clear, bit toggle, bit test—new ALU constants, new multiplication instruction (x squared), biased rounding, result free ALU operations, I/O memory transfers, and global interrupt masking, for increased flexibility.

Fabricated in a high speed, low power, CMOS process, the ADSP-2187L operates with a 25 ns instruction cycle time. Every instruction can execute in a single processor cycle.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1997

### ADSP-2187L

The ADSP-2187L's flexible architecture and comprehensive instruction set allow the processor to perform multiple operations in parallel. In one processor cycle the ADSP-2187L can:

- · Generate the next program address

- Fetch the next instruction

- · Perform one or two data moves

- · Update one or two data address pointers

- · Perform a computational operation

This takes place while the processor continues to:

- Receive and transmit data through the two serial ports

- Receive and/or transmit data through the internal DMA port

- · Receive and/or transmit data through the byte DMA port

- Decrement timer

#### **DEVELOPMENT SYSTEM**

The ADSP-2100 Family Development Software, a complete set of tools for software and hardware system development, supports the ADSP-2187L. The System Builder provides a high level method for defining the architecture of systems under development. The Assembler has an algebraic syntax that is easy to program and debug. The Linker combines object files into an executable file. The Simulator provides an interactive instruction-level simulation with a reconfigurable user interface to display different portions of the hardware environment.

A PROM Splitter generates PROM programmer compatible files. The C Compiler, based on the Free Software Foundation's GNU C Compiler, generates ADSP-2187L assembly source code. The source code debugger allows programs to be corrected in the C environment. The Runtime Library includes over 100 ANSI-standard mathematical and DSP-specific functions.

The EZ-KIT Lite is a hardware/software kit offering a complete development environment for the entire ADSP-21xx family: an ADSP-218x based evaluation board with PC monitor software plus Assembler, Linker, Simulator, and PROM Splitter software. The ADSP-218x EZ-KIT Lite is a low cost, easy to use hardware platform on which you can quickly get started with your DSP software design. The EZ-KIT Lite includes the following features:

- 33 MHz ADSP-218x

- Full 16-bit Stereo Audio I/O with AD1847 SoundPort® Codec

- RS-232 Interface to PC with Windows 3.1 Control Software

- EZ-ICE<sup>®</sup> Connector for Emulator Control

- DSP Demo Programs

The ADSP-218x EZ-ICE<sup>®</sup> Emulator aids in the hardware debugging of ADSP-2187L system. The emulator consists of hardware, host computer resident software and the target board connector. The ADSP-2187L integrates on-chip emulation support with a 14-pin ICE-Port interface. This interface provides a simpler target board connection requiring fewer mechanical clearance considerations than other ADSP-2100 Family EZ-ICEs. The ADSP-2187L device need not be removed from the target system when using the EZ-ICE, nor are any adapters needed. Due to the small footprint of the EZ-ICE connector, emulation can be supported in final board designs.

The EZ-ICE performs a full range of functions, including:

- In-target operation

- Up to 20 breakpoints

- Single-step or full-speed operation

- Registers and memory values can be examined and altered

- PC upload and download functions

- Instruction-level emulation of program booting and execution

- · Complete assembly and disassembly of instructions

- C source-level debugging

See "Designing An EZ-ICE-Compatible Target System" in the *ADSP-2100 Family EZ-Tools Manual* (ADSP-2181 sections) as well as the "Designing an EZ-ICE compatible System" section of this data sheet for the exact specifications of the EZ-ICE target board connector.

#### **Additional Information**

This data sheet provides a general overview of ADSP-2187L functionality. For additional information on the architecture and instruction set of the processor, refer to the *ADSP-2100 Family User's Manual*. For more information about the development tools, refer to the ADSP-2100 Family Development Tools Data Sheet.

#### **ARCHITECTURE OVERVIEW**

The ADSP-2187L instruction set provides flexible data moves and multifunction (one or two data moves with a computation) instructions. Every instruction can be executed in a single processor cycle. The ADSP-2187L assembly language uses an algebraic syntax for ease of coding and readability. A comprehensive set of development tools supports program development.

#### Figure 1. Functional Block Diagram

Figure 1 is an overall block diagram of the ADSP-2187L. The processor contains three independent computational units: the ALU, the multiplier/accumulator (MAC) and the shifter. The computational units process 16-bit data directly and have provisions to support multiprecision computations. The ALU performs a standard set of arithmetic and logic operations; division primitives are also supported. The MAC performs single-cycle multiply, multiply/add and multiply/subtract operations with 40 bits of accumulation. The shifter performs logical and arithmetic shifts, normalization, denormalization and derive exponent operations.

The shifter can be used to efficiently implement numeric format control including multiword and block floating-point representations.

<sup>\*</sup>EZ-ICE and SoundPort are registered trademarks of Analog Devices, Inc.

The internal result (R) bus connects the computational units so that the output of any unit may be the input of any unit on the next cycle.

A powerful program sequencer and two dedicated data address generators ensure efficient delivery of operands to these computational units. The sequencer supports conditional jumps, subroutine calls and returns in a single cycle. With internal loop counters and loop stacks, the ADSP-2187L executes looped code with zero overhead; no explicit jump instructions are required to maintain loops.

Two data address generators (DAGs) provide addresses for simultaneous dual operand fetches (from data memory and program memory). Each DAG maintains and updates four address pointers. Whenever the pointer is used to access data (indirect addressing), it is post-modified by the value of one of four possible modify registers. A length value may be associated with each pointer to implement automatic modulo addressing for circular buffers.

Efficient data transfer is achieved with the use of five internal buses:

- Program Memory Address (PMA) Bus

- Program Memory Data (PMD) Bus

- Data Memory Address (DMA) Bus

- Data Memory Data (DMD) Bus

- Result (R) Bus

The two address buses (PMA and DMA) share a single external address bus, allowing memory to be expanded off-chip, and the two data buses (PMD and DMD) share a single external data bus. Byte memory space and I/O memory space also share the external buses.

Program memory can store both instructions and data, permitting the ADSP-2187L to fetch two operands in a single cycle, one from program memory and one from data memory. The ADSP-2187L can fetch an operand from program memory and the next instruction in the same cycle.

In lieu of the address and data bus for external memory connection, the ADSP-2187L may be configured for 16-bit Internal DMA port (IDMA port) connection to external systems. The IDMA port is made up of 16 data/address pins and five control pins. The IDMA port provides transparent, direct access to the DSPs on-chip program and data RAM.

An interface to low cost byte-wide memory is provided by the Byte DMA port (BDMA port). The BDMA port is bidirectional and can directly address up to four megabytes of external RAM or ROM for off-chip storage of program overlays or data tables.

The byte memory and I/O memory space interface supports slow memories and I/O memory-mapped peripherals with programmable wait state generation. External devices can gain control of external buses with bus request/grant signals (BR, BGH, and BG). One execution mode (Go Mode) allows the ADSP-2187L to continue running from on-chip memory. Normal execution mode requires the processor to halt while buses are granted.

The ADSP-2187L can respond to eleven interrupts. There can be up to six external interrupts (one edge-sensitive, two levelsensitive and three configurable) and seven internal interrupts generated by the timer, the serial ports (SPORTs), the Byte DMA port and the power-down circuitry. There is also a master RESET signal. The two serial ports provide a complete synchronous serial interface with optional companding in hardware and a wide variety of framed or frameless data transmit and receive modes of operation. Each port can generate an internal programmable serial clock or accept an external serial clock.

The ADSP-2187L provides up to 13 general-purpose flag pins. The data input and output pins on SPORT1 can be alternatively configured as an input flag and an output flag. In addition, there are eight flags that are programmable as inputs or outputs and three flags that are always outputs.

A programmable interval timer generates periodic interrupts. A 16-bit count register (TCOUNT) is decremented every *n* processor cycles, where *n* is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

#### **Serial Ports**

The ADSP-2187L incorporates two complete synchronous serial ports (SPORT0 and SPORT1) for serial communications and multiprocessor communication.

Here is a brief list of the capabilities of the ADSP-2187L SPORTs. For additional information on Serial Ports, refer to the *ADSP-2100 Family User's Manual*.

- SPORTs are bidirectional and have a separate, doublebuffered transmit and receive section.

- SPORTs can use an external serial clock or generate their own serial clock internally.

- SPORTs have independent framing for the receive and transmit sections. Sections run in a frameless mode or with frame synchronization signals internally or externally generated. Frame sync signals are active high or inverted, with either of two pulse widths and timings.

- SPORTs support serial data word lengths from 3 to 16 bits and provide optional A-law and μ-law companding according to CCITT recommendation G.711.

- SPORT receive and transmit sections can generate unique interrupts on completing a data word transfer.

- SPORTs can receive and transmit an entire circular buffer of data with only one overhead cycle per data word. An interrupt is generated after a data buffer transfer.

- SPORT0 has a multichannel interface to selectively receive and transmit a 24 or 32 word, time-division multiplexed, serial bitstream.

- SPORT1 can be configured to have two external interrupts (IRQ0 and IRQ1) and the Flag In and Flag Out signals. The internally generated serial clock may still be used in this configuration.

#### **Pin Descriptions**

The ADSP-2187L will be available in a 100-lead TQFP package. In order to maintain maximum functionality and reduce package size and pin count, some serial port, programmable flag, interrupt and external bus pins have dual, multiplexed functionality. The external bus pins are configured during RESET only, while serial port pins are software configurable during program execution. Flag and interrupt functionality is retained concurrently on multiplexed pins. In cases where pin functionality is reconfigurable, the default state is shown in plain text; alternate functionality is shown in italics.

### ADSP-2187L

#### **COMMON-MODE PIN DESCRIPTIONS**

| Pin<br>Norma (a)  | # of<br>Pins | Input/ | Erm etter                                                             |

|-------------------|--------------|--------|-----------------------------------------------------------------------|

| Name(s)           |              | Output | Function                                                              |

| RESET<br>BR       | 1            | I<br>I | Processor Reset Input                                                 |

| $\frac{BR}{BG}$   | 1<br>1       | 1<br>0 | Bus Request Input                                                     |

| BG<br>BGH         | _            | -      | Bus Grant Output                                                      |

|                   | 1            | 0      | Bus Grant Hung Output                                                 |

| DMS<br>PMS        | 1<br>1       | 0      | Data Memory Select Output                                             |

|                   | -            | 0      | Program Memory Select Output                                          |

| IOMS<br>BMS       | 1            | 0      | Memory Select Output                                                  |

| $\frac{BMS}{CMS}$ | 1            | 0<br>0 | Byte Memory Select Output<br>Combined Memory Select Output            |

| $\overline{RD}$   | 1            | 0      | о I                                                                   |

|                   | 1            | -      | Memory Read Enable Output                                             |

| WR<br>WR          | 1            | 0      | Memory Write Enable Output                                            |

| IRQ2/             | 1            | Ι      | Edge- or Level-Sensitive Interrupt<br>Request <sup>1</sup>            |

| PF7               |              | I/O    | Programmable I/O Pin                                                  |

| IRQL0/            | 1            | Ι      | Level-Sensitive Interrupt Requests <sup>1</sup>                       |

| PF6               |              | I/O    | Programmable I/O Pin                                                  |

| IRQL1/            | 1            | Ι      | Level-Sensitive Interrupt Requests <sup>1</sup>                       |

| PF5               |              | I/O    | Programmable I/O Pin                                                  |

| ĪRQE/             | 1            | Ι      | Edge-Sensitive Interrupt Requests <sup>1</sup>                        |

| PF4               |              | I/O    | Programmable I/O Pin                                                  |

| Mode D/           | 1            | Ι      | Mode Select Input—Checked<br>Only During RESET                        |

| PF3               |              | I/O    | Programmable I/O Pin During<br>Normal Operation                       |

| Mode C/           | 1            | Ι      | Mode Select Input—Checked<br>Only During RESET                        |

| PF2               |              | I/O    | Programmable I/O Pin During<br>Normal Operation                       |

| Mode B/           | 1            | Ι      | Mode Select Input—Checked<br>Only During RESET                        |

| PF1               |              | I/O    | Programmable I/O Pin During<br>Normal Operation                       |

| Mode A/           | 1            | Ι      | Mode Select Input—Checked                                             |

| PF0               |              | I/O    | Only During RESET]<br>Programmable I/O Pin During<br>Normal Operation |

| CLKIN,            |              |        | rierina operation                                                     |

| XTAL              | 2            | Ι      | Clock or Quartz Crystal Input                                         |

| CLKOUT            | 1            | 0      | Processor Clock Output                                                |

| SPORT0            | 5            | I/O    | Serial Port I/O Pins                                                  |

| SPORT1            | 5            | I/O    | Serial Port I/O Pins                                                  |

| IRQ1:0            |              |        | Edge- or Level-Sensitive Interrupts,                                  |

| FI, FO            |              |        | Flag In, Flag Out <sup>2</sup>                                        |

| PWD               | 1            | Ι      | Power-Down Control Input                                              |

| PWDACK            | 1            | 0      | Power-Down Control Output                                             |

| FL0, FL1,         |              |        | -                                                                     |

| FL2               | 3            | 0      | Output Flags                                                          |

| VDD and           |              |        |                                                                       |

| GND               | 16           | Ι      | Power and Ground                                                      |

| EZ-Port           | 9            | I/O    | For Emulation Use                                                     |

#### NOTES

<sup>1</sup>Interrupt/Flag Pins retain both functions concurrently. If IMASK is set to enable the corresponding interrupts, then the DSP will vector to the appropriate interrupt vector address when the pin is asserted, either by external devices, or set as a programmable flag.

<sup>2</sup>SPORT configuration determined by the DSP System Control Register. Software configurable.

#### **Memory Interface Pins**

The ADSP-2187L processor can be used in one of two modes, Full Memory Mode, which allows BDMA operation with full external overlay memory and I/O capability, or Host Mode, which allows IDMA operation with limited external addressing capabilities. The operating mode is determined by the state of the Mode C pin during RESET and cannot be changed while the processor is running.

#### FULL MEMORY MODE PINS (MODE C = 0)

| Pin<br>Name(s) |    | Input/<br>Output | Function                                                                                                   |

|----------------|----|------------------|------------------------------------------------------------------------------------------------------------|

| A13:0          | 14 | 0                | Address Output Pins for Program,<br>Data, Byte and I/O Spaces                                              |

| D23:0          | 24 | I/O              | Data I/O Pins for Program, Data,<br>Byte and I/O Spaces (8 MSBs are<br>also used as Byte Memory addresses) |

#### HOST MODE PINS (MODE C = 1)

| Pin<br>Name(s) | # of<br>Pins | Input/<br>Output | Function                                                         |

|----------------|--------------|------------------|------------------------------------------------------------------|

| IAD15:0        | 16           | I/O              | IDMA Port Address/Data Bus                                       |

| A0             | 1            | 0                | Address Pin for External I/O, Pro-<br>gram, Data, or Byte access |

| D23:8          | 16           | I/O              | Data I/O Pins for Program, Data<br>Byte and I/O spaces           |

| IWR            | 1            | Ι                | IDMA Write Enable                                                |

| IRD            | 1            | Ι                | IDMA Read Enable                                                 |

| IAL            | 1            | Ι                | IDMA Address Latch Pin                                           |

| ĪS             | 1            | Ι                | IDMA Select                                                      |

| IACK           | 1            | 0                | IDMA Port Acknowledge Configur-<br>able in Mode D; Open Drain    |

In Host Mode, external peripheral addresses can be decoded using the A0,  $\overline{CMS}, \overline{PMS}, \overline{DMS},$  and  $\overline{IOMS}$  signals

#### Interrupts

The interrupt controller allows the processor to respond to the eleven possible interrupts and reset with minimum overhead. The ADSP-2187L provides four dedicated external interrupt input pins, IRQ2, IRQL0, IRQL1 and IRQE. In addition, SPORT1 may be reconfigured for IRQ0, IRQ1, FLAG\_IN and FLAG\_OUT, for a total of six external interrupts. The ADSP-2187L also supports internal interrupts from the timer, the byte DMA port, the two serial ports, software and the power-down control circuit. The interrupt levels are internally prioritized and individually maskable (except power down and reset). The IRQ2, IRQ0 and IRQ1 input pins can be programmed to be either level- or edge-sensitive. IRQL0 and IRQL1 are level-sensitive and IRQE is edge sensitive. The priorities and vector addresses of all interrupts are shown in Table I.